Funktionale Sicherheit global betrachtet

FPGAs mit integrierten Sicherheitsfunktionen

Entwicklungsingenieure konzentrieren sich oft lediglich darauf, grünes Licht für die Simulation zu bekommen. Geht es aber um Produkte für Märkte, die eine Zertifizierung der funktionalen Sicherheit erforderlich machen, ist es wichtig, das Gesamtbild zu betrachten.

In diesen Fällen ist der Entwicklungsprozess komplizierter. Denn Marketing- und Entwicklungsteams müssen nicht nur ein überzeugendes Produkt entwickeln, sie müssen auch alle geltenden Sicherheitsnormen berücksichtigen, um sicherzustellen, dass das Produkt für den Einsatzzweck geeignet ist. Und diese Normen können spezifisch für den Markt, die Art des Produkts und die Umgebung, in dem es verwendet wird, sein. Diejenigen, die mit diesen Herausforderungen nicht vertraut sind, können auf Unterstützung von externen Ingenieurbüros zurückgreifen.

Die Kunst bei der Entwicklung von funktional sicheren Systemen besteht darin, die geforderten Zertifizierungen mit möglichst geringem Aufwand zu erreichen. Der unabhängige Prüfer muss den Nachweis sehen, dass das Designteam den Standard für funktionale Sicherheit hinsichtlich der systematischen Fähigkeiten und Minderung von zufälligen Hardware-Fehlern auf Grundlage einer glaubwürdigen Gefahren- und Risikoanalyse eingehalten hat. Für das Team kann sich dies wie eine Prüfung anfühlen, allerdings mit der Möglichkeit, die Antworten mit dem Lehrer zu besprechen und sein Feedback umzusetzen, um doch eine akzeptable Lösung zu erreichen. Um die Zertifizierungsaudits zu bestehen, müssen sich die Entwickler-Teams sicher sein, dass der gewählte Designweg erfolgreich ist. Um sie dabei zu unterstützen, hat Xilinx in moderne Validierungsmethoden investiert, die den Anwendern die Sicherheit geben, dass sich die verwendeten Bausteine immer wie vorgesehen verhalten. Damit konnten bereits viele Kunden diesen Prozess erfolgreich abschließen.

Im Bereich der funktionalen Sicherheit ist genau diese Zuversicht entscheidend. Die richtigen Vorstellungen können genau den Unterschied zwischen der Markteinführung eines Produkts und einem umfangreichen Re-Design ausmachen, das möglicherweise auch noch verschiedene Komponenten erfordert, die Zeit brauchen, um zu lernen, wie sie effektiv genutzt werden können. Daher ist es entscheidend, mit Beweisen Vertrauen aufzubauen.

Integrierte funktionale Sicherheit

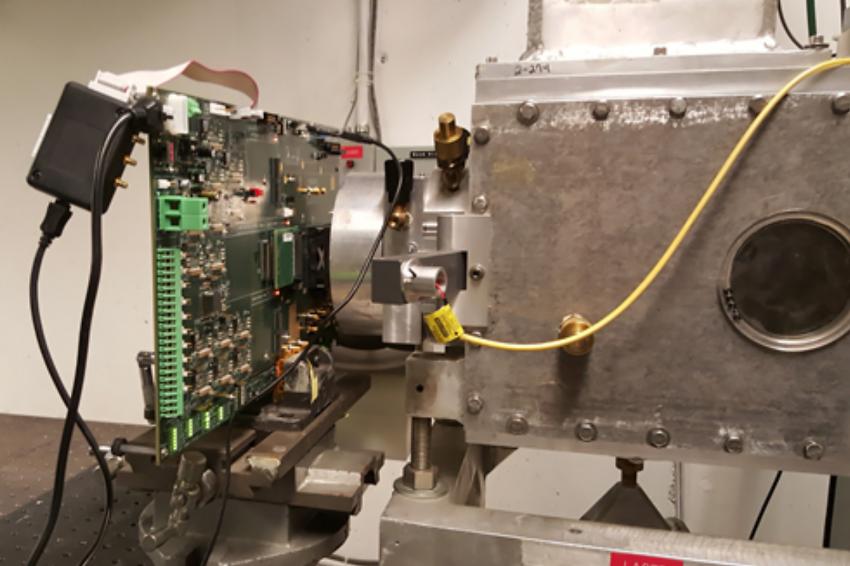

Der Zynq Ultrascale+ MPSoC war der erste Baustein, den Xilinx mit Hinblick auf die funktionale Sicherheit entwickelt hat. Die Kombination aus verbesserten Engineering-Prozessen, dem Testen der Bausteindiagnosefähigkeiten und dem Einbau von Fehlertoleranz gegenüber zufälligen Hardware-Fehlern ermöglichte es, zuverlässige Nachweise über die Fähigkeiten zu liefern, die für interne und externe Bewertungsteams akzeptabel sind.

Daneben ist es aber genauso wichtig zu wissen, was die Komponenten können und was nicht. Aufgrund der Natur von FPGAs muss dem Hardening und Testen des Configuration RAMs (CRAM), also dem SRAM, in dem die Implementierung des Designs gespeichert ist, besondere Aufmerksamkeit geschenkt werden. Externe Zertifizierungsstellen benötigen dementsprechend immer eine diesbezügliche Garantie, wenn sie ein Design mit FPGAs evaluieren. Die dafür eingerichteten Systeme und Verfahren ermöglichen es, sowohl den Nachweis zu erbringen als auch das Verhalten der Bausteine in funktionalen Sicherheitssystemen richtig zu verstehen.

Die bei Xilinx verwendeten SRAM-Techniken nutzen bewährte interne Methoden. Darüber hinaus werden zur Beurteilung der Zuverlässigkeit branchenübliche Jedec-Prüfverfahren eingesetzt. Langzeittests (Rosetta) sowie Neutronentests finden im Los Alamos Science Center (Lance) statt, Protonentests im Crocker Nuclear Laboratory, thermische Neutronentests übernimmt wiederum das McClellan Nuclear Research Center. Darüber hinaus kommen auch Alpha-Partikel-Tests mit einer 232-Thoriumfolie zum Einsatz. Xilinx veröffentlicht diese Daten zweimal jährlich im UG116 Device Reliability Report, den jeder einsehen kann.

Um ein Produkt gemäß den Anforderungen der funktionalen Sicherheit zertifizieren zu lassen, müssen die systematischen Fähigkeiten und die Fehlerrate (FIT: Failure in time) dokumentiert werden. Halbleiterhersteller sollten ihre Kunden im Bereich der funktionalen Sicherheit unterstützen und ihnen Zertifikate vorlegen, die die systematischen Fähigkeiten beim Entwurf der Komponenten und der systematischen Fähigkeiten der Firmware (beispielsweise die Firmware der Xilinx MPSoC-Produkte) bescheinigen. Darüber hinaus erfüllen die zertifizierten Xilinx-Tools die Anforderungen nach SIL 4 (IEC 61508 für den industriellen Markt) bzw. ASLI-D (ISO 26262 für den Automobilmarkt). Damit kann der Kunde sicherstellen, dass die Umsetzung seines Designs den Sicherheitsstandards in Bezug auf die verwendeten Tools entspricht.

Darüber hinaus werden beschleunigte HTOL-Prüfungen (HTOL: High-Temperature Operating Life) genutzt, um permanente Hardwarefehler zu adressieren. Die Ergebnisse dieser Tests werden ebenfalls zweimal jährlich im UG116 Device Reliability Report veröffentlicht. Des Weiteren helfen Diagnosemöglichkeiten auf Siliziumebene oder als Soft-IP für die programmierbare Logik, zufällige Hardwarefehler zu minimieren.

Die Zertifizierung der Vivado-Tools und Compiler bis zum höchsten Sicherheitslevel helfen den Entwicklern bei den systematischen Fähigkeiten. Den Entwicklern stehen außerdem Leitfäden rund um die funktionale Sicherheit zur Verfügung, die sie bei den gewünschten Zertifizierungen unterstützen.

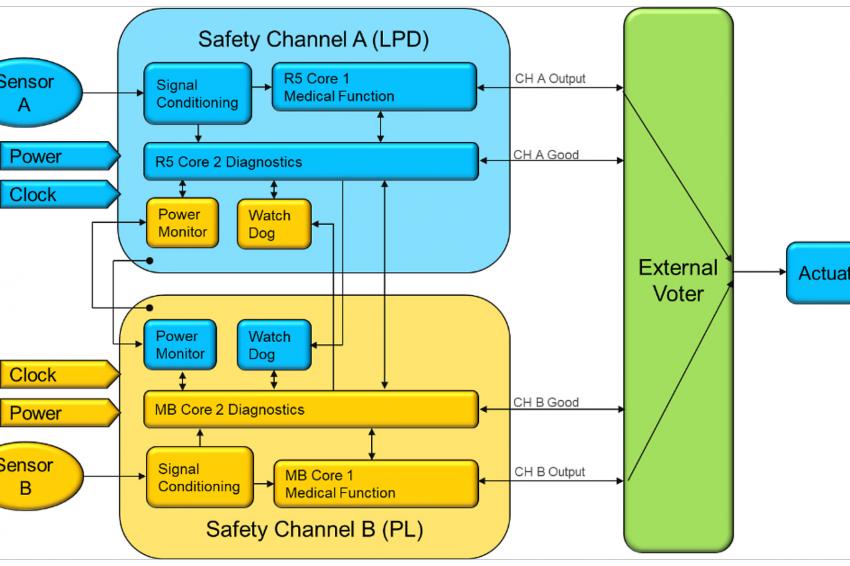

Safety und Single-Chip-Integration

Entwickler von sicherheitskritischen Einrichtungen verlassen sich typischerweise auf eine Systemarchitektur, um systematische und zufällige Hardwareprobleme zu adressieren, die mit einem einzigen Baustein nicht einfach zu lösen sind. Mit den Zynq-Ultrascale+ MPSoCs ist dies nicht notwendig, denn sie stellen die folgenden drei verschiedene Rechenbereiche zur Verfügung: Low Power Domain, Full Power Domain und Programmable Logic Domain. Da jede dieser Domänen unabhängig und heterogen ist, können sie zur Implementierung getrennter Safety-Kanäle verwendet werden und dazu dienen, die Diagnosefähigkeit des Designs durch Redundanz auf demselben Baustein zu verbessern. Damit sind mithilfe von Dekompositionsregeln und Redundanz im Vergleich zu einem Zwei-Chip-Design niedrigere Implementierungskosten möglich sowie eine höhere Zuverlässigkeit des gesamten Interconnects.

Das zweikanalige Design nutzt zwei Domänen im selben Baustein, wobei jede Domäne über einen Lock-Step-Prozessor verfügt. Dadurch wird die Diagnosefähigkeit verbessert, die wiederum benötigt wird, um Diagnosemöglichkeiten in 1002-Architekturen (One out of two) zu unterstützen.

Um die systematischen Fähigkeiten zu verbessern, würde für jede Domäne ein anderes Designteam zum Einsatz kommen, das unterschiedliche CPU-Architekturen und Compiler nutzt. Um die Diagnosefähigkeit zu erhöhen, werden in jeder Domäne Lock-Step-Prozessoren eingesetzt, die durch den gegenseitigen Vergleich per Software weiter verbessert werden, sodass die Fähigkeit zur Erkennung zufälliger Hardwarefehler auf über 99 Prozent erhöht wird. Die Verwendung von zwei Kanälen senkt außerdem die standardbasierte Qualitätsmetrik für jeden Kanal. Dies beschleunigt die Markteinführung und schafft zusätzliche Sicherheit, dass das Produkt erfolgreich zertifiziert werden kann.

Security und Safety in Einklang bringen

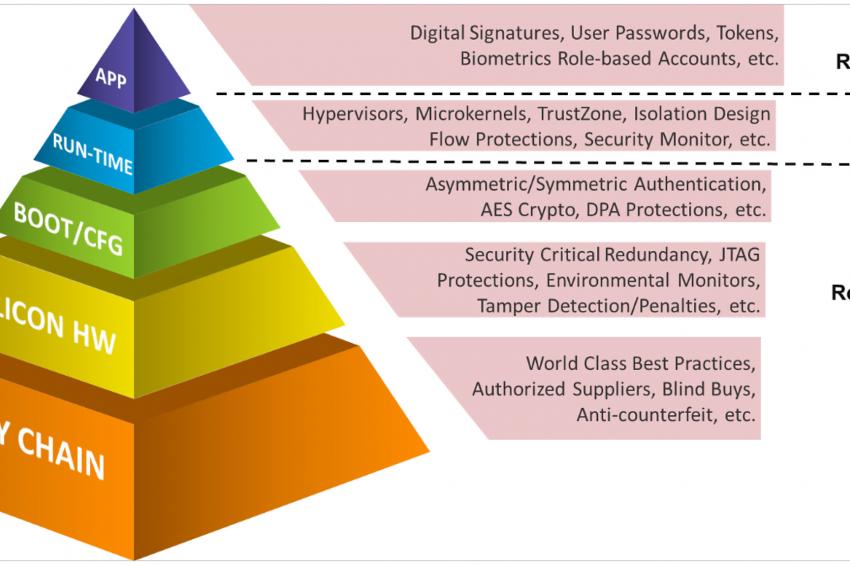

Da die OT- und IT-Bereiche in Unternehmen im Industrial Internet of Things (IIoT) zusammenwachsen, sind Cyberangriffe eine wachsende Bedrohung. Damit ist klar, dass Systeme nicht wirklich funktional sicher sein können, wenn sie nicht auch sicher gegenüber Cyberangriffen sind. An diesem Punkt arbeitet die aktuelle Arbeitsgruppe für funktionale Sicherheit, die die nächste Überarbeitung der Norm IEC 61508 vorantreibt.

Während bei der funktionalen Sicherheit mit Gefahren- und Risikoanalysen gearbeitet wird, wird die Cybersicherheit durch eine Gefahrenanalyse vorangetrieben. Diese Analyse wird verwendet, um die Angriffsfläche des Systems zu identifizieren. Es ist notwendig, die Safety-relevanten Gefahren- und Risikoanalysen und die Security-relevanten Bedrohungsanalysen gleichzeitig durchzuführen, um etwaige Wechselwirkungen zu verstehen. Denn eine isolierte Security-Bewertung kann ernsthafte Folgen für die Safety haben, zum Beispiel eine CPU-Sperrung, Ressourcenbeschränkungen oder andere Sicherheitsmaßnahmen, die den sicheren Betrieb (im Sinne der funktionalen Sicherheit) des Systems gefährden könnten.

In Übereinstimmung mit erfolgreichen Ansätzen zur funktionalen Sicherheit wird die Security-Problematik am effektivsten gemeinsam von Komponentenlieferant und Geräteentwickler übernommen. Dementsprechend hat Xilinx auch die Verantwortung für die Security innerhalb der Lieferkette übernommen. Darüber hinaus hat das Unternehmen Schutzfunktionen auf Siliziumebene und für den Boot-Prozess implementiert, und es stellt Schnittstellen sowie Anleitungen für Laufzeit-Interface, isolierte Designs und empfohlene Designabläufe zur Verfügung. Dies ermöglicht es den Produktentwicklern, ihre Ressourcen auf den Schutz auf Anwendungsebene zu konzentrieren.

Literatur

P. Maillard, J. Arver, C. Smith, O. Ballan, M. J. Hart and Y. P. Chen, „Test Methodology & Neutron Characterization of Xilinx 16nm Zynq UltraScale+ Multi-Processor System-on-Chip (MPSoC),“ 2018 IEEE Radiation Effects Data Workshop (REDW), 2018, pp. 1-4.